# LibreSilicon Standard Cell Library

Hagen Sankowski

October 30, 2022

#### Abstract

Copyright  $\bigcirc 2018$  CHIPFORGE.ORG. All rights reserved.

This process is licensed under the Libre Silicon public license; you can redistribute it and/or modify it under the terms of the Libre Silicon public license as published by the Libre Silicon alliance either version 2 of the License, or (at your option) any later version.

This design is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the Libre Silicon Public License for more details.

For further clarification consult the complete documentation of the process.

## Contents

| 1        | Considerations      | 3  |

|----------|---------------------|----|

| <b>2</b> | Logical Cells       | 4  |

| 3        | Cell AOI21          | 5  |

| 4        | Cell ASYNC1         | 6  |

| 5        | Cell ASYNC2         | 7  |

| 6        | Cell ASYNC3         | 8  |

| 7        | Cell INV            | 9  |

| 8        | Cell martin1989     | 10 |

| 9        | Cell NOR2           | 11 |

| 10       | Cell NOR3           | 12 |

| 11       | Cell sutherland1989 | 13 |

| 12       | Cell vanherkel1991  | 14 |

# 1 Considerations

4 2 LOGICAL CELLS

# 2 Logical Cells

## 3 Cell AOI21

Schematic (one stage,  $1T_p/2T_n$  stacked, 4T total)

6 4 CELL ASYNC1

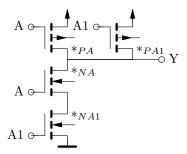

### 4 Cell ASYNC1

Schematic (one stage,  $2T_p/2T_n$  stacked, 12T total)

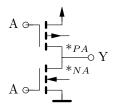

### 5 Cell ASYNC2

Schematic (one stage,  $2T_p/2T_n$  stacked, 8T total)

6 CELL ASYNC3

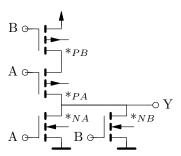

### 6 Cell ASYNC3

Schematic (one stage,  $3T_p/3T_n$  stacked, 12T total)

# 7 Cell INV

Schematic (one stage,  $1T_p/1T_n$  stacked, 17T total)

10 8 CELL MARTIN1989

### 8 Cell martin1989

Schematic (one stage,  $2T_p/2T_n$  stacked, 8T total)

---- o  $\operatorname{net}3$

## 9 Cell NOR2

Schematic (one stage,  $2T_p/1T_n$  stacked, 4T total)

10 CELL NOR3

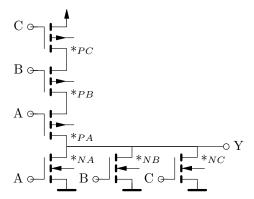

## 10 Cell NOR3

Schematic (one stage,  $3T_p/1T_n$  stacked, 6T total)

# 11 Cell sutherland1989

Schematic (one stage,  $2T_p/2T_n$  stacked, 12T total)

-----o net6

## 12 Cell vanberkel1991

Schematic (one stage,  $3T_p/3T_n$  stacked, 12T total)

——— net5

VDDIO GND ANA