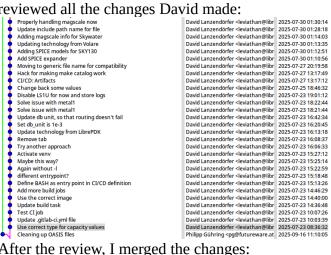

In the last few days I have helped David with the standard cell library generator. At first I have reviewed all the changes David made:

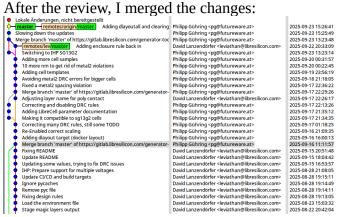

After the review, I merged the changes:

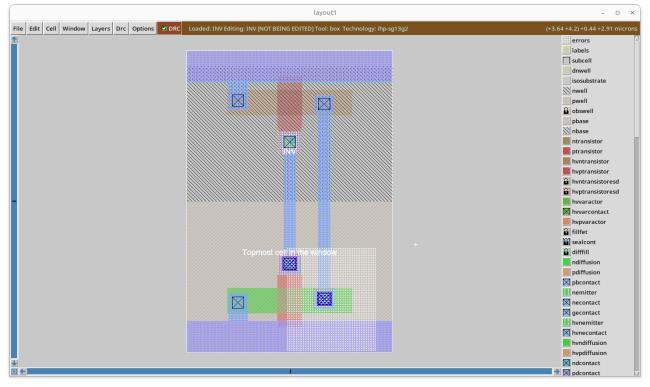

Then I worked through all the DRC design rules for the IHP SG13G2 library, to make the standard cell layouting working for the IHP process. At first I tested it with a simple inverter cell (INV.cell).

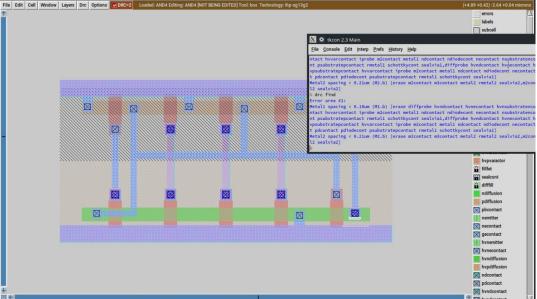

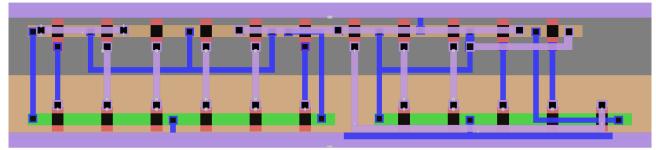

The inverter cell still had some DRC issues, so I reviewed and corrected all the DRC rules and configurations for Iclayout. After those were corrected, the INVerter cell was building correctly, no more DRC errors, and this way the cell would be most likely accepted by the factory.

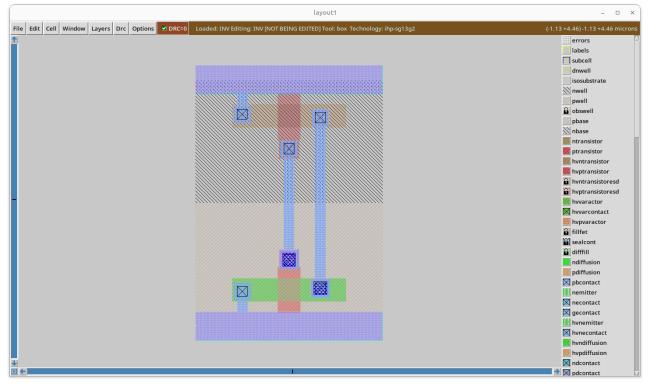

Afterwards I shortly tested a larger AND cell, and discovered that sometimes the vias would be too near to the power rails, so we moved the transistors inwards a few times until all those DRC issues

went away for larger cells. File Edit Cell Window Layers Drc Options

Then we discussed the need for compatibility of our cells with the existing cells supplied by the vendors (like IHP), and we agreed that our cells should be as compatible as feasible, so that they can be mixed&matched with the existing cells. So users of our cells should be able to use both our cells and the cells from the factory within a single design like a RISC-V CPU. Most of the necessary changes to the cells were made to make them compatible, but we havent tested the compatibility yet.

One interesting discovery was that the IHP cells seem to have some margin on the left and right side, which also gets added to our cells in the middle multiple times, so we might be able to shrink our cells a bit, but we have to investigate and try that.

Then I started to run the flow for the whole standard cell library with 656 cells, and we got a speed of approximately 2 of the most complex AOI cells per day, giving a rough estimation of one year to build a whole library on a single laptop. Luckily for our pad cell project we only need INV and NAND2 cells, which can be generated within an hour.

Later on it turned out that AAAAOI3332 (one of the most complex cells) takes more than a week to characterize:

Those complex cells aren't needed for the pad cells though that we are currently working on.

Originally we had planned to create both low and high voltage nfet/pfet models to work with StdCellLib/LibreCell, but it turned out that we only need the low voltage nfet/pfet models for the standard cells, and the voltage level shifting for high-voltage will be done with analog cells in the pad cells, not with standard cells. Therefore we only implemented the 1.8V low voltage nfet/pfet models in our standard cells for SG13G2.

## What we delivered:

- 1) We refactored and brought the StdCell generator up to speed

- 1) Made the basic combinatoric logic for the pad cells work

- 2) Analog characterization of the cells allows for analog simulation of real world applications

During the work, we had a number of ideas for improvements in the future:

- Our Docker container could use a newer TCL version (>=9) for magic, there are some potential runtime issues with our older TCL Version (8.6 I think)

- The 3D visualisation of SG13G2 is missing the wells, we could add them (perhaps in a semi-transparent way?)

- We should define the pins for the power rails only on the top-most power rail layer

- The vias of the power rails seem to be missing, we have to check that they are there

- We could add support for 45° metal routing, which IHP is using. But this seems to be a huge project on its own.

- Reproducible builds (of standard cells) came up again, this time to verify the correctness of optimisations in the SPICE setup and parallelisation

- Support for asymmetric DRC rules in Iclayout, preferably in a deterministic way

- We should test the interoperability of the our SG13G2 cells with the vendor cells

- We want to introduce a feature to automatically add a prefix and/or postfix to all the cell names of the generated cells, but we haven't decided yet, where in the flow that should be done exactly.

- lclayout has some empty net names that should be investigated

- We still get LVS errors in Iclayout's internal LVS, which get ignored by our flow

- We currently only have lctime working, CharLib seems to have issues with the SG13G2 PDK and needs further investigation.

- One idea to improve the characterization speed is to implement a SPICE caching server

- Both CharLib and letime are crashing reproducibly during the characterization of our cells